FPGAが時々動かない??-ステート・マシンのデッドロック-

FPGAにおけるステート・マシン(FSM)のエンコード方式は?

今回は、FPGAを構成する重要な要素の一つである、LUTについて解説したいと思います。

目次

順番に説明していきます。

論理ゲート → 組合わせ回路 → LUT という順だと理解しやすいと思います。

論理ゲートはロジックを構成するための基本となるものです。ここでいう「ロジック」とは実現させたい機能というニュアンスです。例えば、地震が起こった時、コンロの火は危ないのですぐに消したいですよね。この場合、地震センサーからの入力を\(a\)、コンロの火を出力\(y\)とすれば、\(y = \bar{a}\)としたいです。すなわち、NOTゲート1つで実現できるロジックということになります。

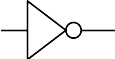

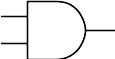

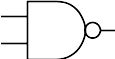

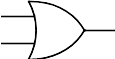

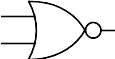

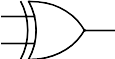

論理ゲートの例を図1に示します。(同図の論理ゲート以外にもあります)

入力\(a\)、\(b\)と出力\(y\)の関係は図1中の表の通りです。なお、この表のことを真理値表といいます。

| a | y |

| 0 | 1 |

| 1 | 0 |

| a | b | y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| a | b | y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| a | b | y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| a | b | y |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

| a | b | y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

図1 論理ゲートの例

上記の地震とコンロの例のように論理ゲート1個で済むロジックはまれで、実際のロジックはもっと複雑です。例えば、工作機械であれば、油圧が正常(= 1)かつ、空気圧が正常(= 1)かつ、人の手検知センサーが未検知(= 0)(けが防止)の時だけ動く…とか。さらに、もしモードBのならば(if~)、ユーザーがボタンを押して(= 1)いるときだけ動く…とかです。

この場合は、基本の論理ゲートを組み合わせてロジックを実現することになります。この、論理ゲートを組み合わせて作る回路を、組合わせ回路(combination circuit)といいます。

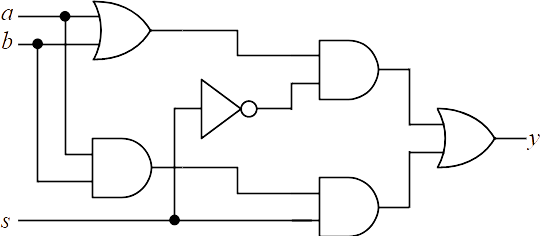

それでは、簡単な組合わせ回路を見てみましょう。以下のロジックは、図2の組合わせ回路になります。

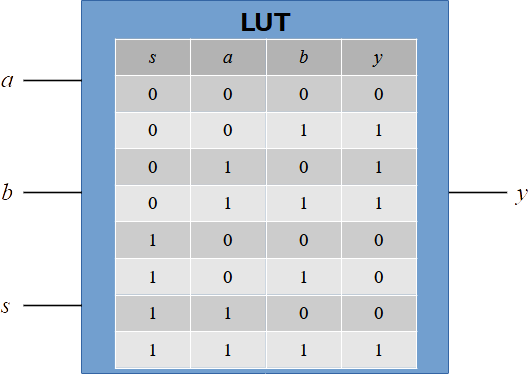

いきなりVerilog HDLのコードを出しましたが、何となく意味は分かるかと思います。スイッチ\(s\)が0の時は入力\(a\)、\(b\)の論理和を出力、スイッチ\(s\)が1の時は入力\(a\)、\(b\)の論理積を出力、という回路です。

1 2 3 4 5 6 | always @ (s or a or b) begin if (s == 1'b0) y <= a | b; else y <= a & b; end |

図2のような組合わせ回路によってロジックを実現したいわけです。しかし、FPGAの中身は、沢山のANDゲートとかORゲートがあるという作りにはなっていません。

では、どうするかというと、真理値表です。すなわちLUTが図3のように設定されることで所望の組合わせ回路を実現します。(FPGA内のLUTやそのほかのブロックを設定することを、コンフィグレーションといいます)

ということで、LUTとは、組合わせ回路を実現するブロックです。